ATmega32 – 8 Bit AVR Microcontroller

AVR microcontrollers operate on an advanced RISC architecture. ATmega32, a low power CMOS 8-bit microcontroller, is constructed upon the AVR enhanced RISC architecture. When the cycle frequency reaches 1MHz, the AVR is capable of executing 1 million instructions per second.

Key Features:

32 x 8 registers for general working purposes.

32 kilobytes of in-system self-programmable flash program memory.

2 kilobytes of internal SRAM.

1,024 bytes of EEPROM.

Available in 40-pin DIP, 44-lead QTFP, 44-pad QFN/MLF packages.

32 programmable I/O lines.

8-channel, 10-bit ADC.

Two 8-bit timers/counters featuring separate prescalers and compare modes.

One 16-bit timer/counter with separate prescaler, compare mode, and capture mode.

4 PWM channels.

In-system programming facilitated by an on-chip boot program.

Programmable watchdog timer with a distinct on-chip oscillator.

Programmable serial USART.

Master/slave SPI serial interface.

Special Microcontroller Features:

Six slumber modes: Idle, ADC noise reduction, power-save, power-down, standby, and extended standby.

Internally calibrated RC oscillator

Interrupt sources from external and internal origins

Power-on reset and customizable brown-out detection.

The Arithmetic Logic Unit (ALU) is directly linked to all 32 registers, enabling the simultaneous access of two independent registers in a single instruction performed within a single clock cycle.

The power-down feature preserves the register contents while halting the oscillator. All other functionalities of the chip remain inactive until an external interrupt occurs. The asynchronous timer enables users to sustain a timer operation in power-save mode while the remaining device remains in a dormant state.

In ADC noise reduction mode, the CPU and all I/O modules, except the ADC and asynchronous timer, are halted. Standby mode puts the entire device, except the crystal oscillator, into a sleep state. However, both the main oscillator and asynchronous timer continue to function in extended standby mode.

The ATmega32 stands out as a potent microcontroller due to its in-system self-programmable flash integrated onto a single chip. This feature offers a highly adaptable and cost-effective solution for various embedded control applications.

Pin Descriptions:

VCC: Power supply for digital voltage

GND: Ground connection

Port A (PA7-PA0): This port functions as analog inputs for the A/D converter. Additionally, it operates as an 8-bit bidirectional I/O port when the A/D converter is unused.

Port B (PB7-PB0) & Port D (PD7-PD0): Both are 8-bit bidirectional I/O ports. Their output buffers demonstrate symmetrical drive characteristics, providing high sink and source capabilities. When used as inputs, these ports are strongly pulled low if the pull-up resistors are engaged. They also accommodate various special function features of the ATmega32.

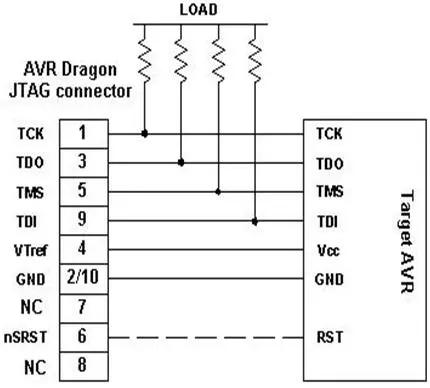

Port C (PC7-PC0): Another 8-bit bidirectional I/O port. If the JTAG interface is activated, the pull-up resistors on pins PC5 (TDI), PC3 (TMS), and PC2 (TCK) will be enabled.

Reset: This serves as an input.

XTAL1: Functions as an input to the inverting oscillator amplifier and also acts as an input to the internal clock operating circuit.

XTAL2: Serves as an output from the inverting oscillator amplifier.

AVCC: Designated as the supply voltage pin for Port A and A/D converter. It requires connection to VCC.

AREF: AREF represents the analog reference pin utilized by the A/D converter.

ATmega32 Memories:

The ATmega32 incorporates two primary memory spaces: data memory and program memory. Additionally, it includes an EEPROM memory designed for data storage purposes.

In System Programmable Flash Program Memory:

The ATmega32 incorporates 32Kbytes of on-chip in-system reprogrammable flash memory designed for program storage. The flash memory is structured as 16k X 16 and segmented into two sections: the Boot program section and the application program section.

SRAM Data Memory:

The lower 2144 data memory locations manage the Register file, I/O memory, and internal data SRAM. Within this range, the initial 96 locations handle the Register file and I/O memory, while the subsequent 2048 locations cater to the internal data SRAM. These data memory locations utilize five distinct addressing modes: direct, indirect with displacement, indirect, indirect with pre-decrement, and indirect with post-decrement. Through these addressing modes, access is granted to the 32 general-purpose registers, 64 I/O registers, and 2048 bytes of internal data SRAM.

EEPROM Data Memory:

It comprises 1024 bytes of data EEPROM memory, accessible as an independent data space allowing for the reading and writing of individual bytes.

I/O Memory:

The I/O space houses all inputs/outputs (I/Os) and peripherals. Access to these I/O locations is facilitated through the IN and OUT instructions, allowing data transfer between the 32 general-purpose registers and the I/O space. I/O registers within the address range of 00-1F can be directly accessed on a bit level using the SBI and CBI instructions.

ATmega8

Introduction

This microcontroller, part of the AVR family manufactured by Atmel Corporation in 1996, operates on an 8-bit CMOS architecture following the RSIC (Reduced Instruction Set Computer) design. Its primary advantage lies in the absence of an accumulator, allowing the storage of operation results in any register as defined by the instruction.

Architecture

Memory

It comprises 8KB of flash memory, 1KB of SRAM, and 512 Bytes of EEPROM. The 8K flash is divided into two segments: the lower part serves as the boot flash section, while the upper part functions as the application flash section. Within the SRAM, there are 1K bytes available, including 1120 bytes allocated for general-purpose and I/O registers. The initial 32 address locations are designated for 32 general-purpose 8-bit registers. The following 64 addresses are specifically allocated for I/O registers. All these registers are directly linked to the ALU. The EEPROM is utilized for storing user-defined data.

Input/output ports

The system encompasses a total of 23 I/O lines distributed across three distinct I/O ports labeled as B, C, and D. Specifically, Port B incorporates 8 I/O lines, Port C contains 7 I/O lines, and Port D comprises 8 I/O lines.

The registers associated with each respective port (referred to as Port X, denoted by B, C, or D) are as follows:

– DDRX: Data Direction Register for Port X

– PORTX: Data Register for Port X

– PINX: Input Register for Port X

Timers and Counters

It comprises three timers featuring similar modes. Among these, two timers operate with an 8-bit capacity, while the third operates as a 16-bit timer.

Oscillators

It includes an internal reset feature and oscillator, negating the necessity for external inputs. The internal RC oscillator can generate an internal clock that operates at programmable frequencies of 1MHz, 2MHz, 4MHz, or 8MHz. Additionally, it accommodates an external oscillator with a maximum frequency of 16MHz.

Communication

The device facilitates both synchronous and asynchronous data transfer mechanisms via its USART (Universal Synchronous and Asynchronous Receiver Transmitter), enabling communication with modems and other serial devices. Additionally, it supports the SPI (Serial Peripheral Interface) for inter-device communication, operating on the master-slave methodology. Another supported communication protocol is the TWI (Two-Wire Interface), allowing connectivity between any two devices using only 2 wires and a common ground connection.

Furthermore, it incorporates a comparator module within the chip, enabling voltage comparison between two inputs of the Analog comparator through external connections.

Moreover, it features a 6-channel ADC, with 4 channels boasting 10-bit accuracy and 2 channels offering 8-bit accuracy.

ATmega Pin Diagram:

A significant attribute of the ATmega8 is that, apart from 5 pins, all other pins have the capability to support two signals simultaneously.

Port C utilizes pins 23, 24, 25, 26, 27, 28, and 1, whereas port B uses pins 9, 10, 14, 15, 16, 17, 18, and 19, and port D uses pins 2, 3, 4, 5, 6, 11, and 12.

Pin 1 functions as the Reset pin, initiating a reset when a low-level signal persists longer than the minimum pulse length.

Pins 2 and 3 serve as serial communication ports for USART. Pins 4 and 5 are employed as external interrupts, each triggering based on the set interrupt flag bit of the status register and the continuous existence of the interrupt condition, respectively.

Pins 9 and 10 function as external oscillators and timer counters. Pin 10 specifically caters to a crystal oscillator or a low-frequency crystal oscillator. If the internal calibrated RC oscillator serves as the clock source while the asynchronous timer is enabled, these pins transform into timer oscillator pins.

Pin 19 operates as the Master Clock output and slave clock input for the SPI channel. Pin 18 serves as the Master clock input and slave clock output. Pin 17 is designated as the Master data output and slave data input for the SPI channel, also functioning as an output compare match output when enabled, acting as an external output for the timer/counter compare match.

Pin 16 operates as a slave select input and can be configured as a timer/counter1 compare match by setting PB2 pin as an output. Pin 15 can serve as an external output for timer/counter compare match A.

Pins 23 to 28 are allocated for ADC channels. Additionally, pin 27 can function as a Serial Interface clock, and pin 28 can serve as a serial interface data input. Pins 13 and 12 are utilized as Analog Comparator inputs, while pins 11 and 6 act as timer/counter sources.

Microcontroller Sleep Modes

The Microcontroller features six distinct sleep modes.

Idle Mode: This mode halts the CPU’s operation while permitting the functionality of SPI, USART, ADC, TWI, Timer/Counter, interrupts system, achieved by setting the MCU register flag’s SM0 to SM2 bits to zero.

ADC Noise Reduction Mode: It ceases CPU operation but allows the ADC, external interrupts, timer/counter2, and watchdog to function.

Power-down Mode: This mode facilitates external interrupts, the 2-wire serial interface, and watchdog while disabling the external oscillator, effectively stopping all generated clocks.

Power-save Mode: Utilized when the Timer/Counter is asynchronously clocked, this mode suspends all clocks except for clkASY.

Standby Mode: In this mode, the oscillator operates while pausing all other operations.

Applications Involving Atmega8

Blinking LED

The software is scripted in C language and initially compiled as a .c file. Following this, the ATMEL software tool transforms this file into a binary ELF object file. Subsequently, it undergoes a conversion process to become a hex file. Finally, the hex file is transferred to the microcontroller using the AVR dude program.