The electrolytic capacitor is far from being the most reliable electronic component. One of its failure modes – a gradual loss of capacity – can hardly be noticed until power supply malfunction occurs. Thus, any chance to monitor the condition of the filter capacitors of an electronic device in situ would be a useful thing.

This simple Design Idea monitors capacitor voltages during power-down, and records out-of-spec conditions to available NVRAM/EEPROM.

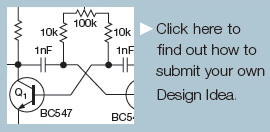

The only resources needed are a microcontroller, ADC, and a bit of non-volatile memory space, meaning for most systems, there’s essentially no extra cost or componentry required. Figure 1 shows only one monitoring channel, but of course multiple voltages could be checked (e.g., both VIN and multiple VOUT levels of the regulators).

When power-off (P_OFF) is signaled to the system, the µC disables interrupts and all significant (and unpredictable) power consumers in the circuit.

The µC can then estimate the filter capacitance by timing how long it takes for the voltage to drop a certain amount. Alternatively, the routine can measure the voltage difference before and after a fixed time.

In either case, there must be enough leeway between the minimum VOUT of all supplies, and the minimum operating voltages required by the µC to allow enough time for measurements.

If any measured value is not within limits, the µC writes diagnostic data to the NVRAM, which can be acted upon at the next power-up.

R1 and R2 function to both match the ADC input range and to be the main “test load” for capacitor discharge; the supply current drawn by the active circuitry will likely be too variable to rely on.

For more detail: Capacitor self-diagnostics