Okay firstly the reason I wrote about the clock system instead of I/O ports or something else in this second post of the XMega series is simply because of the fact that without understanding clock configurations you won’t get what you want from your chip. Since XMega’s clock system is software-level configurable and complex at first, it makes itself the first priority module before anything else.

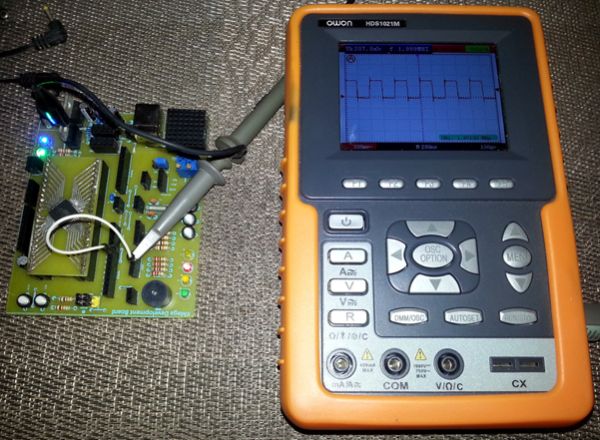

There are several clock sources that XMega micros can use as clock. These are both internal and external clock sources. As stated earlier, clocks are not set by fuse settings unlike traditional Mega AVRs, they are controlled by software and the outputs from these sources can be multiplied using the internal Phase Locked-Loop (PLL). Thus there’s a wide range of clocks available in the XMega and it’ll not be needed to shut down and reprogram the XMega just to change its clock – a great relief from meddling with fuse settings. Some port pins can also output the system clock frequency. Literally there’s no need to depend on external quartz crystals which are not available in all frequencies.

There are several clock sources that XMega micros can use as clock. These are both internal and external clock sources. As stated earlier, clocks are not set by fuse settings unlike traditional Mega AVRs, they are controlled by software and the outputs from these sources can be multiplied using the internal Phase Locked-Loop (PLL). Thus there’s a wide range of clocks available in the XMega and it’ll not be needed to shut down and reprogram the XMega just to change its clock – a great relief from meddling with fuse settings. Some port pins can also output the system clock frequency. Literally there’s no need to depend on external quartz crystals which are not available in all frequencies.

A bird’s eye view of the XMega clock system’s block diagram tells us what we are allowed to use as clock sources and which peripherals run with which clock source(s). It may appear complex but it is actually very easy to understand. If you don’t get it initially don’t worry about it.

The four internal clock sources apart from external sources that connect to XTAL and TOSC pins and these are:

The four internal clock sources apart from external sources that connect to XTAL and TOSC pins and these are:

Any clock source can have more than one use. For example a clock source can provide the clock that drives the CPU and it can also drive another peripheral, e.g. a timer-counter. It is also possible run a number of different clock sources even if none are used as system clock.

There are hardware-level protections that prevent conflicting issues as well as prevent wrong clock selections. To change device clock frequency, the desired clock frequency is set first and then the Configuration Change Protection (CCP) register is configured to disable security for protected I/O register after the source has stabilized because clock-related registers are a part of protected I/O.

Internal or external clock sources can be used as reference sources to the PLL in order to generate higher frequencies. An accurate good quality 32.768 KHz external crystal on TOSC pins or the internal 32.768 kHz oscillator can be used to calibrate the internal 2MHz and 32MHz sources. For calibration purpose the internal Digital Frequency-Locked Loops (DFLL) hardware are used.

External clock sources include typical crystal oscillators/resonators, electronic clock generator circuits, etc. Maximum external crystal frequency is 16MHz but can be increased with PLL. However external clock sources can’t be calibrated since there’s no way an XMega chip has prior knowledge about this source unlike internal clock sources.

There are hardware-level protections that prevent conflicting issues as well as prevent wrong clock selections. To change device clock frequency, the desired clock frequency is set first and then the Configuration Change Protection (CCP) register is configured to disable security for protected I/O register after the source has stabilized because clock-related registers are a part of protected I/O.

Internal or external clock sources can be used as reference sources to the PLL in order to generate higher frequencies. An accurate good quality 32.768 KHz external crystal on TOSC pins or the internal 32.768 kHz oscillator can be used to calibrate the internal 2MHz and 32MHz sources. For calibration purpose the internal Digital Frequency-Locked Loops (DFLL) hardware are used.

External clock sources include typical crystal oscillators/resonators, electronic clock generator circuits, etc. Maximum external crystal frequency is 16MHz but can be increased with PLL. However external clock sources can’t be calibrated since there’s no way an XMega chip has prior knowledge about this source unlike internal clock sources.

For more detail: XMega Clock System