The ARINC 818 video protocol since its inception has gained wide adoption on large aircrafts such as Airbus A350XWB, Boeing 787, KC46A, and many others. ARINC 818 protocol is used to provide point to point, high-speed, low-latency video transmission for mission-critical systems such as cockpit display, video processors, cameras, and IR sensors. Offering high-speed ARINC 818 interfaces in FPGA arises many challenges due to low-latency and synchronous timing requirements for most displays.

iWave Systems, being the leading FPGA design house, offers an extensive portfolio of FPGA IP Cores. And one of the most predominant being ARINC 818 IP. Today, we are excited to announce the successful implementation of iWave’s ARINC 818 IP Core on Microsemi PolarFire FPGA devices. The PolarFire devices offer the highest security, small form factor, flash-based FPGA, that consume 50% low power competing to mid-range FPGA’s.

Key features include:

- Fully compliant with ARINC 818-2 standards

- Can be used for both transmit and receive applications

- Flexible streaming video interface

- Configurable ADVB video formats(resolution, pixel type, etc.)

- Supports progressive and interlaced video formats

- IP parameters can be configured as per customers interface control document(ICD)

- Transmission medium – either optical or copper

The ARINC 818-2 complaint PolarFire FPGA evaluation kit is suitable for various high-performance applications and functionalities that include communication, military, aviation. With strong competence in FPGA, iWave Systems has demonstrated the seamless integration of iWave’s ARINC 818-2 IP transmitter and receiver functionality on Microsemi’s PolarFire FPGA evaluation kit.

Demo description:

- FPGA Platform: Microsemi PolarFire FPGA EVK

- FMC card: Multi-video interface Add on FMC card iW-EMELA-PC-01-R1.0

- HDMI Monitor: To display the video output

Demo: External loopback test

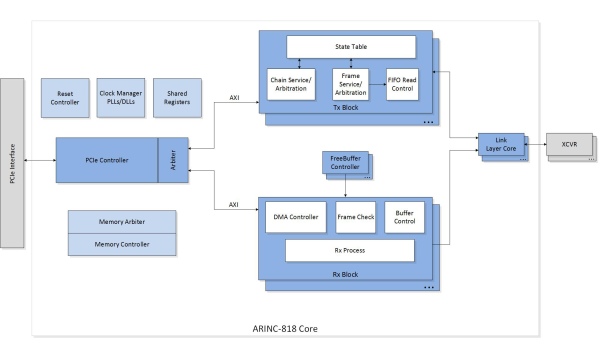

The ARINC 818-2 IP transmitter block receives the video data generated by the internal test pattern generator and converts it into ADVB frames. These ADVB frames are sent out through an FPGA transceiver that is connected to the SFP module. These ADVB frames are looped back to the Rx channel via the SFP module, which is then decoded by the ARINC 818-2 IP receiver block to retrieve the video data and is then displayed on the HDMI monitor.

Read more: IWAVE UNVEILS THE IMPLEMENTATION OF ARINC 818-2 IP CORE ON MICROSEMI POLARFIRE FPGA